"Interconnect Stress Test (IST) is a testing method that complies with IPC TM650 2.6.26 standards. It involves heating test samples through current application to achieve thermal cycling, rapidly verifying the reliability of printed circuit boards. Using a 1000-cycle example, this test can be completed in just 5 days. IST testing has become widely accepted and utilized in the printed circuit board industry.

Arcanum Advanced Inc. offers IST testing services tailored to customer test conditions. If there is currently no IST test sample design, you can also contact our sales for assistance with the design.

Testing conditions:

1. Precondition : 245~260°C x 6 cycles

2. Supported Sample Types : Single/Dual Testing

3. IST Testing Temperature : 150~220°C (190~220°C for Microvias)

4. Cycle Count : 500~9999 cycles

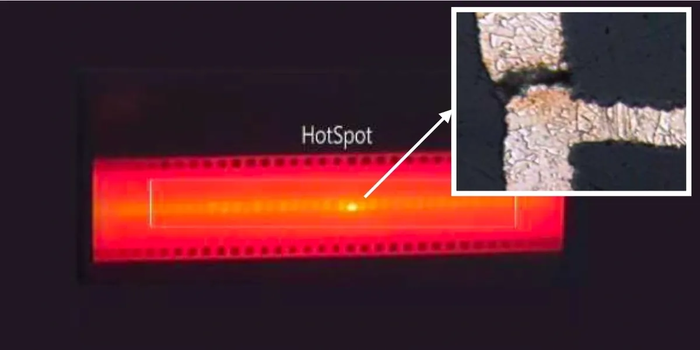

- Thermal Camera

Utilizing thermal imaging methods that allows the identification of unintended failure locations on test samples, facilitating subsequent failure analysis.

- Delamination

DELAM employs a capacitance measurement method to determine whether there is delamination or layer separation within the board. In IST test samples, an inner layer with a flat copper surface is designed, with adjacent layers forming a flat capacitor. By measuring the capacitance values before and after testing, one can assess the presence of physical delamination or material degradation.

Feedback list